3行でわかる今回のニュース

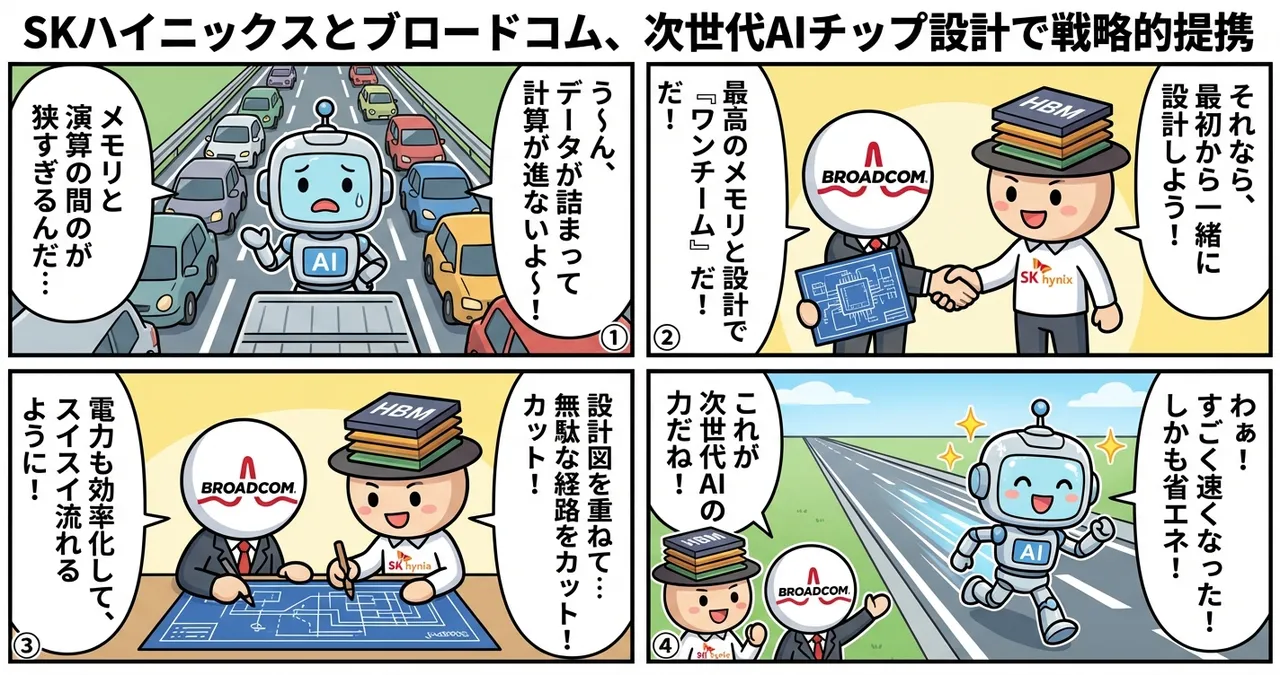

- SKハイニックスとブロードコムが、次世代AIチップ設計における戦略的提携を発表しました。

- メモリ(HBM)とAIアクセラレータを開発の初期段階から統合し、電力効率と性能を飛躍的に高めます。

- 既存のコンポーネントを組み合わせる手法から、システム全体を最適化する「ワンチーム」体制への転換を目指します。

もうちょっと詳しく

業界の巨頭が手を組んだ「シリコン・アライアンス」

2月13日、韓国のSKグループ会長と、米半導体大手ブロードコム(Broadcom)のホック・タンCEOが会談し、AI半導体分野での緊密な協力関係を築くことで合意しました。

これまで、メモリを作る会社(SKハイニックス)と、演算チップ(AIアクセラレータ)を設計する会社(ブロードコムなど)は、それぞれの規格に合わせて製品を開発し、後から組み合わせるのが一般的でした。しかし、今回の提携では「設計の初期段階」から両者が情報を共有します。

なぜ今、統合が必要なのか

現在のAI開発において、最大のボトルネックは「メモリ帯域」と「消費電力」です。どれだけ演算速度が速くても、メモリからのデータ転送が追いつかなければ宝の持ち腐れになってしまいます。

SKハイニックスが持つ世界最高峰のHBM(高帯域幅メモリ)技術と、ブロードコムの高度なASIC(特定用途向け集積回路)設計技術を融合させることで、これら物理的な限界を突破しようという狙いがあります。

なにがすごいの?

今回の提携の核心は、「個別最適」から「全体最適」へのシフトにあります。以下の比較表を見ると、その意義が分かりやすいでしょう。

| 特徴 | 従来の設計アプローチ | 今回の「ワンチーム」体制 |

|---|---|---|

| 開発プロセス | 各パーツを独立して開発 | 初期段階からメモリとロジックを同時設計 |

| データ転送 | 標準規格による接続(ロス発生) | チップ間通信を極限まで最適化 |

| 電力効率 | 汎用的な設計のため、無駄が多い | 特定のAI処理に特化した低消費電力化 |

| 拡張性 | 物理的な配置に制約がある | 次世代パッケージング技術での高密度化 |

特に、次世代規格となるHBM4以降では、メモリの一部にロジック機能を搭載する「カスタムHBM」の重要性が増しています。この領域でブロードコムの設計力が加わることは、競合他社に対して大きなアドバンテージになるはずです。

日本の開発現場への影響

日本のエンジニアや企業にとっても、このニュースは無関係ではありません。

まず、データセンターの運用コストに直結します。より電力効率の高いチップが登場すれば、国内で進むAI専用データセンターの構築において、冷却コストや受電容量の課題が緩和される可能性があります。

また、ブロードコムは多くの日本企業とも取引があるため、彼らのカスタムチップ(ASIC)ソリューションを通じて、日本独自のAIモデルに最適化されたハードウェアを調達しやすくなる未来も想像できます。ハードウェアの進化を前提とした、より大規模なモデル開発の計画が立てやすくなるでしょう。

試してみたいポイント

ハードウェアの話ではありますが、開発者として意識しておきたいアクションをまとめました。

- HBM4のロードマップを確認する: 2025年後半から2026年にかけて登場するHBM4が、どのようにソフトウェアの並列処理に影響するか予習しておきましょう。

- カスタムASICのトレンドを追う: NVIDIA一強の時代から、特定の用途に絞った「カスタムチップ」へと比重が移りつつある流れを把握しておくと、インフラ選定の視野が広がります。

- 推論コストの再計算: 新世代チップによる電力効率の向上が、将来的にAPI利用料金やインスタンス費用にどう還元されるか、コストシミュレーションを更新する準備をしておきましょう。

まとめ

SKハイニックスとブロードコムの提携は、単なる製品供給を超えた「AIインフラの再定義」とも言える動きです。メモリと演算が溶け合うような新しいチップ設計が、私たちの手元に届くAIのスピードをさらに加速させてくれるでしょう。ハードウェアの進化がソフトウェアの可能性をどこまで広げるのか、今から楽しみですね。